## EE330 Spring 2024 Homework 6 Solutions

Problem 1: Assume a resistor has a resistance of 1kn at T = 300°k. If the TCR of this resistor is constant of value 2000ppm/oc, what will be the resistance at T = 350° k7.

$$\frac{\text{Solution}}{\text{R}(T_2) = R(T_1) \left[ 1 + (T_2 - T_1) \frac{\text{T}cR}{10^6} \right]} =$$

$$R(350^\circ k) = R(300^\circ k) \left[ 1 + (350 - 300) \frac{2000}{10^6} \right]$$

$$R(350^\circ k) = 1000 \left[ 1 + (50 \times \frac{2000}{10^6}) \right] = 1100 \Omega = 1.1 \text{ kSL}$$

## 2.

We got the value of resistivity based on the doping density.

Doping density

$$\rightarrow 5 \times 10^{4} \text{ cm}^{3}$$

Resistivity  $\rightarrow 9.045 \text{ cm}^{3}$

$R = \rho L = 9.045 \times 0.2 = 24.12 \text{ ks}^{2}$

$WH = 0.015 \times 0.005$

$$\frac{2 \operatorname{mob} \operatorname{lem} 4}{\operatorname{Uning}} \operatorname{Voltage} \operatorname{divider}, \quad \operatorname{Vout} = \frac{\frac{1}{e^{C}}}{R + \frac{1}{e^{C}}} \operatorname{Vin}$$

$$3 \operatorname{dB} \operatorname{frequency} = \operatorname{Cut} \operatorname{off} \operatorname{frequency} = f_{e} = 10 \operatorname{MHz}$$

$$\Rightarrow \quad f_{e} = \frac{1}{2\overline{11}Rec}$$

$$\Rightarrow \quad C = \frac{1}{2\overline{11}Rf_{e}} = \frac{1}{2\overline{11}\times10\times10^{3}\times10\times10^{6}} = 1 \cdot \operatorname{SP2} \times 10^{6^{12}} = 1 \cdot \operatorname{SP2} p \operatorname{F}$$

$$\Rightarrow \quad \operatorname{Uning} \quad R(\overline{T_{2}}) = R(\overline{T_{1}}) \left[1 + (\overline{T_{2}} - \overline{T_{1}}) \frac{2300}{10^{6}}\right]$$

$$= (\overline{T_{2}}) = (\overline{T_{1}}) \left[1 + (\overline{T_{2}} - \overline{T_{1}}) \frac{1000}{10^{6}}\right]$$

the temperature value pairs for each resistor can be found as -> At 273K, R = 10KSL, C = 1.592pF and the 3dB frequency = 10MHz -> AE 350K, R = 11.771K.D., C=1.715pF and 3dB frequency = 7.88 MHz

so the graphs will look as thown below with the 3dB frequency or cut off frequency as calculated above.

(b)

°(o change in 3dB frequency =

$$10 \text{ M} \text{Hz} - 7.88 \text{ M} \text{Hz} \times 100\%$$

$10 \text{ M} \text{Hz}$

$= 21.2\%$

-

PS) What is the range in the diode current?

$$I_{D} = J_{S}A e^{\frac{N_{D}}{e^{NVt}}} V_{DE} 0.5 V \text{ or } 0.6$$

$J_{S} = 10^{-15} A/u^{2} V_{E} 26 mV$

$A = 50 u^{2}$

0.5 V

$$\frac{0.6V}{I_0 = 10^{-15} / \mu^2 \cdot 50 u^2} e^{\frac{0.6V}{24 n V}}$$

$$I_0 = 526.199 u^4$$

The range in the diode current is between

$$Vx = I_0 \cdot R + V_0$$

$$V_0 = a \cdot 6V$$

$$V_1 = I_0 \cdot 2K + 0.6V$$

$$I_0 = I_0 \cdot 2K + 0.6V$$

5.

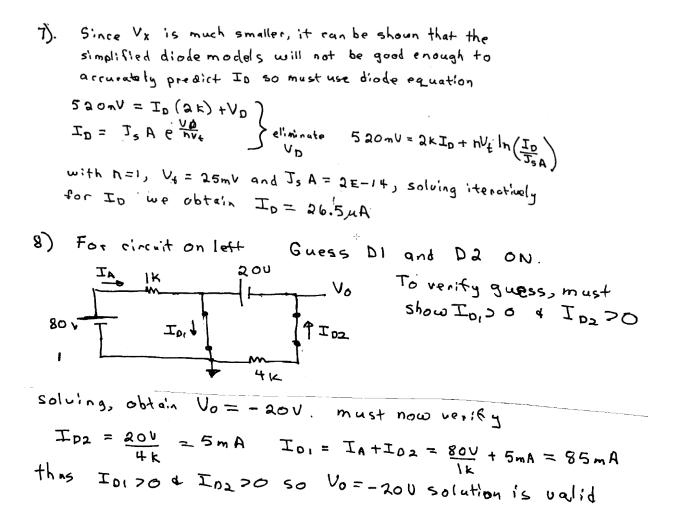

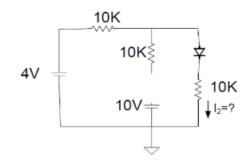

## For the right circuit:

I will start by assuming the middle diode is off, and the rightmost diode is on. This guess is made on the assumption that the location of the 10V source relative to the 4V source will cause currents to flow in the wrong directions. This allows us to treat the middle diode as an open circuit, giving us the following diagram.

As the 10V source drives an open circuit and the  $10k\Omega$  resistor ends at an open circuit, we can neglect them. Using KVL, we can find the current through the loop using the following equation:

$$4V - (i_2 * 10k\Omega) - 0.7V - (i_2 * 10k\Omega) = 0$$

This should reduce down to  $i_2 = \frac{3.3V}{20k\Omega} = 165\mu A$ , which gives a 1.65V drop across each resistor. Additionally, this gives a voltage of 2.35V at the anode of the rightmost diode. With the 10V source at the cathode of the middle diode, this would make the voltage across the middle 10k $\Omega$  resistor and diode -7.65V, meaning current would be flowing the wrong direction through the diode and confirming the initial assumption that it is off. This gives us the result of  $i_2 = 165\mu A$ .

Problem 10

**a** .

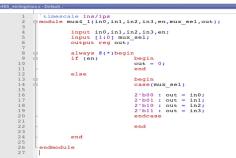

207/ee Ln#

//initiation of module //initiation of input bits //initiation of select pin for mux // initiation of output //starts for any change values //active low input =1 //active low output

// for selecting a mux pin

//assigning values based on select pin

| Ln#             | <u> </u> | · /      |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|-----------------|----------|----------|-----------|-----------|---------|--------|---------|----------|--------|---------|---------|---------|-----------|------|---|---|

|                 | 1        |          | le 1ns/1p |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 2 6      | module m | ux_4_1_th | <b>);</b> |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 3        |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 4 🔺      | :        | reg [1:0] | mux s     | sel;    |        |         |          | //inpu | ts are  | initia  | ited as | regis     | ters |   |   |

|                 | 5        |          |           | -         |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 6 🔺      |          | reg in0,i | n1,in2    | 2,in3,e | n;     |         |          |        |         |         |         |           |      |   |   |

|                 | 7        |          |           | · ·       | · ·     |        |         |          |        |         |         |         |           |      |   |   |

|                 | 8        |          | wire out; |           |         |        |         |          | //outp | uts are | e initi | ated    | as wir    | es   |   |   |

|                 | 9        |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 10       | ,        | mux4 1 du | t(in0.    | in1 in  | 2.in3. | en mux  | sel.ou   | t):    | //inf   | itiatic | n of d  | ut        |      |   |   |

|                 | 11       |          |           |           |         | 2,110, |         |          | -,,    | ,,      | LOIGOIG | n or a  | u c       |      |   |   |

|                 | 12       |          | i         | nitial    | in0 =   | 0.     |         |          |        |         |         |         |           |      |   |   |

|                 | 13       |          |           |           | in1 =   |        |         |          |        |         |         |         |           |      |   |   |

|                 | 14       |          |           |           | in2 =   |        |         |          |        |         |         |         |           |      |   |   |

|                 | 15       |          |           |           | in3 =   |        |         |          |        |         |         |         |           |      |   |   |

|                 | 16       |          |           |           | en =    |        |         |          |        |         |         |         |           |      |   |   |

|                 | 17       |          |           |           | mux s   |        | 1000    |          |        |         |         |         |           |      |   |   |

|                 | 18       |          | L         | Interat   | s       | er – 2 | 1000    |          |        |         |         |         |           |      |   |   |

|                 |          |          | _         |           | #1      | 1.0    |         |          | 0.1.   |         |         |         |           |      |   |   |

|                 | 19       |          | ē         | liways    | #1 mux  | _sel[0 | ] = ~mu | x_set    | 0];    |         |         |         |           |      |   |   |

|                 | 20       |          | ē         | iiways    | #2 mux  | _set[1 | ] = ~mu | x_set    | 1];    |         |         |         |           |      |   |   |

|                 | 21       |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 22       |          | ĉ         | ilways    | #4 en   | = ~en; |         |          |        |         |         |         |           |      |   |   |

|                 | 23       |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          | endmodul | e         |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 25       | I        |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | 26       |          | ·         |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 | -        | Mana     |           |           |         |        |         | <u> </u> |        |         |         |         |           |      |   |   |

|                 |          | Msgs     |           |           |         |        |         |          | 1      |         |         |         | L         |      |   |   |

| /mux_4_1_tb/mux | 2'h3     |          | 3         | 10        | 1       | 2      | 3       | 10       | 1      | 2       | 3       | lo      | <u>[1</u> | 2    | 3 | 0 |

| /mux_4_1_tb/in0 | 1'h0     |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

| /mux 4 1 tb/in1 | -No I    | Data-    |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

| /mux 4 1 tb/in2 |          | Data-    |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

| /mux_4_1_tb/in3 |          | Data-    |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

| /mux_4_1_tb/en  |          | Data-    |           | -         |         |        |         |          |        |         |         |         |           |      |   |   |

| /mux_4_1_tb/out | -No [    | Data-    |           | ]         |         |        |         |          |        | ]       |         | ]       |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      |   |   |

|                 |          |          |           |           |         |        |         |          |        |         |         |         |           |      | _ |   |

| <pre>module</pre> | <pre>demux4_1(in,op0,op1,op2,</pre> | op3,demux_sel,en);       | //initiation of module                        |  |  |  |  |  |  |  |

|-------------------|-------------------------------------|--------------------------|-----------------------------------------------|--|--|--|--|--|--|--|

|                   | input in,en;                        |                          | //initiation of input pins                    |  |  |  |  |  |  |  |

|                   | input [1:0] demux sel;              |                          | //intitiation of select pin for demux output  |  |  |  |  |  |  |  |

|                   |                                     |                          |                                               |  |  |  |  |  |  |  |

|                   | output reg op0,op1,op2,             | op3;                     | //initiation of outputs                       |  |  |  |  |  |  |  |

| Ь.                | always @(*) begin                   |                          | <pre>// starts for any change in values</pre> |  |  |  |  |  |  |  |

| 白                 | if (en)                             | begin                    | // active low input = 1                       |  |  |  |  |  |  |  |

|                   |                                     | op0 = 0;                 | -                                             |  |  |  |  |  |  |  |

|                   |                                     | op1 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op2 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op3 = 0;                 |                                               |  |  |  |  |  |  |  |

| F                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

| $\perp$           |                                     |                          |                                               |  |  |  |  |  |  |  |

|                   | else                                | begin                    |                                               |  |  |  |  |  |  |  |

| 보                 |                                     | case(demux_sel)          | //for different selections the output is      |  |  |  |  |  |  |  |

| 무                 |                                     | 2'b00:begin<br>op0 = in; | <pre>// received at a different pin</pre>     |  |  |  |  |  |  |  |

|                   |                                     | op0 = 1n;<br>op1 = 0;    |                                               |  |  |  |  |  |  |  |

|                   |                                     | op1 = 0;<br>op2 = 0;     |                                               |  |  |  |  |  |  |  |

|                   |                                     | op3 = 0;                 |                                               |  |  |  |  |  |  |  |

| L                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

| L.                |                                     | 2'b01:begin              |                                               |  |  |  |  |  |  |  |

| Ϋ́                |                                     | op0 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | opl = in;                |                                               |  |  |  |  |  |  |  |

|                   |                                     | op2 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op3 = 0;                 |                                               |  |  |  |  |  |  |  |

| F                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

| Ь.                |                                     | 2'b10:begin              |                                               |  |  |  |  |  |  |  |

|                   |                                     | op0 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op1 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op2 = in;                |                                               |  |  |  |  |  |  |  |

|                   |                                     | op3 = 0;                 |                                               |  |  |  |  |  |  |  |

| F                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

| 卓                 |                                     | 2'bll:begin              |                                               |  |  |  |  |  |  |  |

|                   |                                     | op0 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op1 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op2 = 0;                 |                                               |  |  |  |  |  |  |  |

|                   |                                     | op3 = in;                |                                               |  |  |  |  |  |  |  |

| -                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

|                   |                                     | endcase                  |                                               |  |  |  |  |  |  |  |

| L                 |                                     | end                      |                                               |  |  |  |  |  |  |  |

| L.                | end                                 | d                        |                                               |  |  |  |  |  |  |  |

| endmodu           |                                     |                          |                                               |  |  |  |  |  |  |  |

|                   |                                     |                          |                                               |  |  |  |  |  |  |  |

## h /home/ha1207/ee465\_verilog/demux\_tb.v (/demux\_tb) - Default\* \_\_\_\_\_ timescale lns/lps 2 pmodule demux\_tb(); 3 4 5 reg in, en; reg [1:0] demux\_sel; //inputs are initiated as registers 6 7 8 wire op0,op1,op2,op3; //outputs are initiated as wires 9 10 11 12 13 14 15 16 17 18 19 demux4\_1 dut(in,op0,op1,op2,op3,demux\_sel,en); //initiation of dut initial in =1; initial en =0; initial demux\_sel = 2'b00; always #1 demux\_sel[0] = ~demux\_sel[0]; //toggle the bit 0 every cycle always #2 demux\_sel[1] = ~demux\_sel[1]; //toggle the bit 1 every 2 cycles always #4 en = ~en; //toggle the enable pin every 4 clock cycles 20 21 22 endmodule

| <pre>       /demux_tb/en       /demux_tb/demux </pre> | 1'h1<br>1'h0<br>2'h2<br>1'h0 | 2 | 3 |      | 0    | 1 |      | 2    | 3 |      | 0    |

|-------------------------------------------------------|------------------------------|---|---|------|------|---|------|------|---|------|------|

|                                                       | 1'h0                         |   |   |      |      |   |      |      |   |      |      |

| 💠 /demux_tb/op2                                       | 1'h1                         |   |   |      |      |   |      |      |   |      |      |

| /demux_tb/op3                                         | 1'h0                         |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

|                                                       |                              |   |   |      |      |   |      |      |   |      |      |

| 🛎 📰 💿 📃 Now                                           | 100000 ps                    |   |   | 8800 | 0 ps |   | 9000 | 0 ps |   | 9200 | 0 ps |

| 💼 🎤 😑 Cursor 1                                        | 98998 ps                     |   |   |      |      |   |      |      |   |      |      |